# european space agency

european space research and technology centre

WSM/SH/010 Issue 1 February 1996

# VHDL Models for Board-level Simulation

Prepared by S. Habinc

Spacecraft Control and Data Systems Division (WS) Keplerlaan 1 - Noordwijk - The Netherlands Mail address: Postbus 299 - 2200 AG Noordwijk - The Netherlands Tel: +31-71-565 4722 - Telex: 39098 - E-mail: sandi@ws.estec.esa.nl - Fax: +31-71-565 4295 Page intentionally left blank

Copyright © 1995 European Space Agency. All rights reserved. This document may be used and distributed without restrictions provided that this copyright statement is retained and that any derivative work acknowledges the origin of the information.

# **Table of contents**

| 1<br>1.1<br>1.2<br>1.3<br>1.4                            | INTRODUCTION<br>Purpose and scope<br>Document organisation<br>References<br>Conventions                                                                                                                                                                      | 5                                |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 2<br>2.1<br>2.2<br>2.3                                   | BOARD-LEVEL SIMULATION<br>Definition of board-level simulation<br>Benefits of board-level simulation<br>Board-level simulation using VHDL                                                                                                                    | 8                                |

| 3<br>3.1<br>3.2<br>3.2.1<br>3.2.2                        | MODELS FOR BOARD-LEVEL SIMULATION<br>Hierarchy<br>Functional modelling<br>Modelling for functional accuracy<br>Modelling for simulation performance                                                                                                          | 11<br>13<br>13<br>14             |

| 3.2.3<br>3.2.4<br>3.3<br>3.3.1<br>2.2.2                  | Evaluation of simulation performance<br>Outline of entity and architecture declarations for functional cores<br>Interface modelling<br>Timing modelling                                                                                                      | 22<br>24<br>24                   |

| 3.3.2<br>3.3.3<br>3.3.4                                  | Management of unknown input values<br>Reporting model messages<br>Outline of entity and architecture declarations for models                                                                                                                                 | 39                               |

| 4<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.4 | VERIFICATION OF MODELS FOR BOARD-LEVEL SIMULATION<br>Test bench<br>Test object<br>Test generator and result checker<br>Verification of functionality<br>Verification of interfaces<br>Verification result compression<br>Evaluation of verification coverage | 43<br>45<br>46<br>48<br>51<br>52 |

| 5<br>5.1<br>5.2                                          | MODELLING AND SIMULATING BOARD DESIGNS<br>Board designs in VHDL<br>Verification of board designs                                                                                                                                                             | 55                               |

| 6<br>6.1<br>6.2                                          | DESIGN DOCUMENTATION<br>User's Manual<br>Supplement                                                                                                                                                                                                          | 62                               |

| APPENDIX A: OUTLINE OF USER'S MANUAL                     |                                                                                                                                                                                                                                                              | 64<br>65                         |

|                                                          | APPENDIX B:MULTIPLE-INPUT SIGNATURE REGISTERAPPENDIX C:TIMING PARAMETER TYPES                                                                                                                                                                                |                                  |

| APPENDIX D: ABBREVIATIONS                                |                                                                                                                                                                                                                                                              | 70                               |

Page intentionally left blank

# 1 INTRODUCTION

#### **1.1 Purpose and scope**

This document provides recommendations for development and usage of VHDL models intended for board-level simulation. This document is intended to be read together with the VHDL Modelling Guidelines, RD1. It could be used in ESA developments of models for board-level simulation and for simulation of board designs comprising such models.

The information herein is not to be considered as requirements, although sometimes expressed as such, but merely as useful hints and recommendations.

The purpose of these recommendations is to define modelling criteria that will produce models for board-level simulation that are highly accurate in both functionality and timing, and that will provide sufficient simulation performance to facilitate long simulation runs. The document also provides sufficient information to allow someone with little VHDL knowledge to perform a simulation of a board design using models for board-level simulation.

Parts of the document, such as the discussion on model verification, can also be used for ASIC developments. Requirements on models for board-level simulation and VHDL models used for synthesis are dissimilar and therefore are no synthesis aspects discussed in this document. The document does not address distribution of models for board-level simulation nor the protection of design information, issues which are discussed in "The Usage of VHDL in the European Space Agency", RD6.

This document is not intended to be a guide to the VHDL language itself. On the contrary is the reader expected to have previous VHDL knowledge before developing a model intended for board-level simulation.

#### **1.2** Document organisation

This document is divided in five major parts, the first one covering the definition and benefits of board-level simulation, followed by guidelines for developing models for board-level simulation. The third part covers the verification of these model, and is followed by a description on how to model and verify a board design. The final part specifies requirements on model documentation.

For each requirement or suggestion stated in the document there is normally an accompanying explanation and often a code example or a figure. All code examples in the document have been taken from a complete model for board-level simulation, although the VHDL code may sometimes have been reduced to highlight the essential parts. The code examples are therefore not always possible to be analysed by a VHDL simulator as presented. A complete model is not included in the document due to the prohibitive size of the source code, but is made available via *ftp* as described in section 1.3.

#### 1.3 References

This document is available from ESA in the PostScript format via *ftp* at URL ftp://ftp.estec.esa.nl/pub/vhdl/doc/BoardLevel.ps.

Additional information on board-level simulation, including a complete example, is available at URL http://www.estec.esa.nl/wsmwww/vhdl/boardlevel.html.

The following documents are being referenced:

| RD1 | VHDL Modelling Guidelines,                                               |

|-----|--------------------------------------------------------------------------|

|     | P. Sinander, ESA ASIC/001, European Space Agency, The Netherlands, 1994, |

|     | URL ftp://ftp.estec.esa.nl/pub/vhdl/doc/ModelGuide.ps                    |

| RD2 | IEEE Standard VHDL Language Reference Manual,                            |

|     | IEEE Std 1076-1993, IEEE, New York, USA, 1994                            |

| RD3 | IEEE Standard Multivalue Logic System for VHDL Model Interoperability    |

|     | (Std_logic_1164), IEEE Std 1164-1993, IEEE, New York, USA, 1993          |

| RD4 | IEEE Standard VITAL ASIC Modelling Specification, Version 3.0,           |

|     | IEEE, New York, USA, URL http://vhdl.org/vi/vital                        |

| RD5 | Built-In Test for VLSI: Pseudorandom Techniques,                         |

|     | P. H. Bardell et al., John Wiley & Sons, New York, USA, 1987             |

| RD6 | The Usage of VHDL in the European Space Agency,                          |

|     | P. Sinander, European Space Agency, The Netherlands, 1995,               |

|     | URL ftp://ftp.estec.esa.nl/pub/vhdl/doc/UseOfVHDL.ps                     |

| RD7 | VHDL Coding Styles and Methodologies: an In-Depth Tutorial,              |

B. Cohen, Kluwer Academic Publishers, USA, 1995

### 1.4 Conventions

A *component model* in this document is a gate level netlist or a synthesisable Register Transfer level, RTL, description, in VHDL or any other notation, representing the logic design from which the component has been manufactured and being suitable for simulation.

The types and subprograms declared in the packages *ESA.Simulation* defined in RD1, *Std.Standard* and *Std.TextIO* defined in RD2, *IEEE.Std\_Logic\_1164* defined in RD3, and *IEEE.Vital\_Timing* and *IEEE.Vital\_Primitives* defined in RD4, will be addressed in this document without necessarily further stating their origin or in which package they belong.

## 2 BOARD-LEVEL SIMULATION

This section defines board-level simulation and describes its benefits and limitations. By knowing the purpose and characteristics of models intended for board-level simulation it is more likely that such a simulation will be successful. Knowing what can and cannot be achieved using board-level simulation can reduce unprofitable efforts in advance.

#### 2.1 Definition of board-level simulation

Board-level simulation can be defined as simulating the functionality of one or several printed circuit boards built with standard components, possibly incorporating Application Specific Integrated Circuits, ASIC, and Application Specific Standard Products, ASSP. Board-level simulation is also known under the names rapid or virtual prototyping and sometimes system simulation. The purpose of board-level simulation is to verify the behaviour of the board design, e.g. that the components operate correctly in the selected operating modes.

When board designs contain processors it is also possible to perform verification of the hardware-software interaction, such as verifying that ASIC registers can be programmed and software drivers work properly etc. In addition, the performance of the processor board could be evaluated. Board-level simulation will also give some information about timing correctness, though it can probably not replace worst-case timing analysis.

Board-level simulation does not comprise verification of individual ASICs during their development. It does not comprise system performance simulation including aspects such as throughput, latency, buffer allocation and utilisation, where neither accurate data nor clock behaviour is considered being essential.

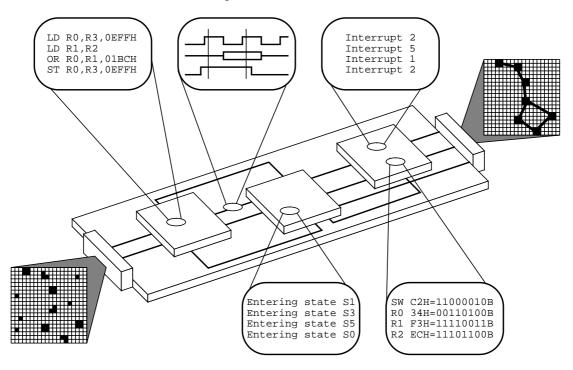

Figure 1: The designers view of a board design when using board-level simulation.

#### 2.2 Benefits of board-level simulation

The feasibility and benefits of board-level simulation have already been proven in several projects. It supports a top-down methodology, allowing simulation of boards not fully implemented, enabling the designer to work with incomplete specifications of the own system or component and facilitates early verification of the design requirements. It also allows the designer to explore different design solutions and to prototype manageable parts of larger systems.

Product specifications can be verified before any manufacturing or breadboarding is started. This is useful when defining a system or component in a proposal or to ensure that when a breadboard is built it does not contain functional errors.

When designing an ASIC, its operation in a board design can be verified before manufacture. If models intended for board-level simulation are provided before the first silicon, significant savings in schedule can be obtained.

Integration can be performed earlier and the first design and verification loop can be done without any hardware manufacturing. The manufacturing can be postponed until all specifications have settled and all interfaces have been verified. It permits full laboratory integration without any available hardware, allowing the first integration to be done earlier in the design. The designer can deliver a board design comprising models for board-level simulation to the user for early system verification.

Special-built equipment for check-out and unit or system testing, which is nowadays as complex as the actual design, can be modelled as well. Allowing the prototype and the test equipment to be simulated together before any of them are built, which can reduce interfacing problems, or even reduce the need for the test equipment being built.

Models for board-level simulation allow the test engineer to simulate situations that are difficult to capture in real hardware due to timing synchronisation etc., resulting in a more thorough verification of the board design. Board-level simulation provides the designer with unlimited probing and acquisition points, not always possible to realise for the hardware.

Models for board-level simulation provide limited simulation support during parallel development of hardware and software, since this type of simulations usually take long time to perform, but delivers high functional and timing accuracy. However, it has been shown that by carefully selecting which software parts to simulate the time spent simulating can be reduced to manageable lengths. It is perhaps not always feasible to boot a complete operating system and launch applications, but all the firmware and hardware drivers could be verified using board-level simulation.

Board-level simulation enables hardware and software designers to work together in an early stage and to solve interfacing problems before committing the hardware for manufacturing. This area of simulation will become more interesting with the continuously increasing speed of simulators.

Board-level simulation should be carefully planned. Time spent modelling and simulating has to be weighted against what can be gained or lost compared to the replaced or reduced non-simulation activities. Efficient use of board-level simulation can lead to the reduction of other design activities.

It is important to establish by whom the board design model development and simulation should be performed while planning the activity to prevent unnecessary educational costs induced by assigning engineers to the task with no VHDL experience, even though only little experience is actually needed.

#### 2.3 Board-level simulation using VHDL

A major issue for board-level simulation is the availability of simulation models of the components used in the board design. Despite commercial models being available for many standard components, increasingly often ASSPs, ASICs and other unusual components are used. Hardware modellers can solve this problem, though they are expensive, complicated to use and have limitations in the number of components that can be used simultaneously.

Using VHDL models is therefore an interesting alternative when no other models are available, which is the typical case for almost all components used on board spacecraft. By using VHDL the effort to support several platforms and simulators is greatly reduced, since VHDL models require no or only minor modifications for each new simulator.

It has been demonstrated that VHDL models of components can be integrated together to design and debug embedded systems in their entirety using hardware-less design methodology. Due to VHDL simulator performance reasons board-level simulation is normally limited to the digital domain.

Using VHDL for board-level simulation enables the user to also perform true mixed-level simulation, since detailed models are mostly written in VHDL and the number of ASIC libraries written in VHDL is rapidly increasing. Still, all different models have to follow some guidelines to ensure interoperability. This document and RD1 form such guidelines. The board design simulation can also contain non-VHDL representations such as netlists or schematics, being useful when verifying a board design containing an ASIC for which no VHDL library exists.

It is important to establish by whom the simulation models should be provided, which can become a critical issue if there is no model for board-level simulation available. A survey of existing models has therefore to be performed well before the simulation begins, allowing for the development of missing models.

#### **3 MODELS FOR BOARD-LEVEL SIMULATION**

A model for board-level simulation is characterised by its accurate modelling of the component behaviour, simulation performance, and ease of use for board designers. All such models delivered to ESA should be developed in accordance with RD1, and their implementation could benefit from following the suggestions made in this document.

The behaviour of the model as seen from the outside should be the same as for the modelled component and should include the full functionality, though specific test modes only used for manufacturing test need not be implemented. The interface signals of the model should have the exact waveform behaviour as observed for the component. Since the internal structure and state of the model do not need to reflect the modelled component, internal signals should not be used during the analysis of acquired simulation results since they could provide information not being fully correct.

A model for board-level simulation should be verified against a *component model* when possible, which could be in VHDL or any other representation suitable for simulation. The purpose of the verification should be to ensure the correctness of the model w.r.t. the component behaviour. When no other representation of the component is available for simulation, the model verification should be based on the information found in a Data Sheet or similar. Each model intended for board-level simulation should be provided with a test bench verifying its behaviour, which is described further in section 4.

Bus functional models, sometimes called bus interface models, are considered being reduced models for board-level simulation, modelling only the timing and behaviour of the interfaces. The timing and format of output drivers for data/control/addresses etc. are modelled as accurately as possible, while the internal functionality of the component is not necessarily modelled at all. Using bus functional models does not provide the full potential of board-level simulation since they simulate only a portion of the component. Nevertheless, the development of such models should follow the suggestions made herein since they should be possible to use together with models for board-level simulation.

The simulation performance should be assessed when transforming a model written on the Register Transfer level, RTL, to a model intended for board-level simulation. The assessment can be supported by comparing the source code with the requirements in this document. RTL models do normally not have sufficient simulation performance and will need to be modified since they are normally written for synthesis which imposes conflicting requirements on the VHDL code w.r.t. models for board-level simulation. The main development effort would then be to optimise the code accordingly, and to implement the model interfaces and develop the verification test bench.

Experience has shown that a proper review of the requirements in RD1 should be performed before a development begins and each model should be reviewed thoroughly before being released.

The source code header of the model entity should contain all information necessary for the user to simulate the model in a board design, and is also allowing distribution of analysed models containing no source code. A User's Manual should be delivered with every model intended for board-level simulation, as specified in section 6.1.

### 3.1 Hierarchy

Hierarchy for models is introduced to obtain good source code readability and to separate different modelling aspects. The outlined hierarchy scheme below is based on two of these aspects, namely timing and functionality. Since these usually stem from two different lines of documentation and representation, the Data Sheet and the *component model*, the model intended for board-level simulation should be partitioned taking this into account. A partitioning also enables separate verification of the two domains of the model.

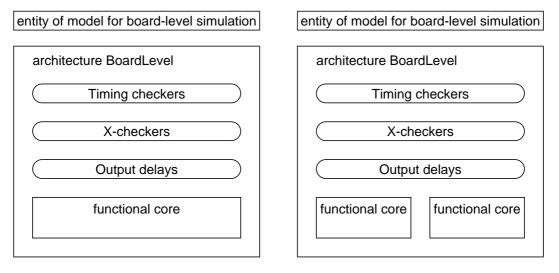

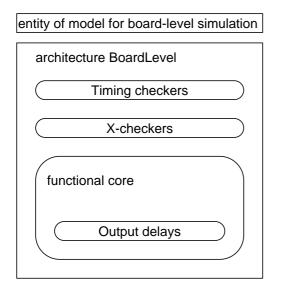

The model should be divided in two hierarchical levels; the top-level architecture and its functional core, to clearly separate the timing and checking for unknown input values from the functionality aspect of the model, as shown in figure 2. It is recommended that there are no other than these two hierarchical levels in the model, since multiple levels could reduce the code readability if not carefully used. The top-level architecture should be independent of the functional core where possible to reduce the need for changing it if only the functionality needs to be modified.

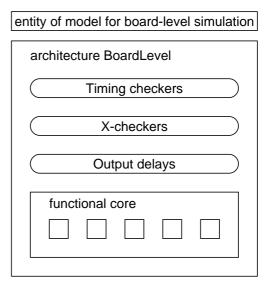

The two-level hierarchy could be flattened for improving simulation performance by reducing the number of signals interconnecting the hierarchy, although it is not recommended. This approach should only be used in extreme cases or for small models, and is shown in figure 3.

Multiple entities comprising a functional core

# **Figure 2:** *Preferred two-level hierarchies (squares with rounded corners are processes or concurrent procedures, regular squares are subcomponents).*

The functionality of the component should be modelled in the functional core, excluding any timing aspects and without internal delays. A functional core could comprise more than one entity for larger designs, each functional block would then be a component instantiated in the top-level architecture. There should not be more components for the functional core than there are blocks in the architectural block diagram. In the functional core comprises many modules, which could be the case when a model is based on an RTL model, an additional hierarchy level could be considered, as shown in figure 3. These modelling aspects will be further referenced as *functional modelling*.

Process comprising a functional core in a one-level hierarchy

Sub-entities comprising a functional core in a three-level hierarchy

#### **Figure 3:** *Optional one- and three-level hierarchies.*

The external timing of the model should be contained in the top-level architecture, including setup and hold time checking, clock-to-output and propagation delay scheduling. It could be modelled in the functional core when simulation performance is critical and when source code readability is not reduced. Management of unknown input values can be divided between the two hierarchical levels as described section 3.3.2. These modelling aspects will be further referenced as *interface modelling*.

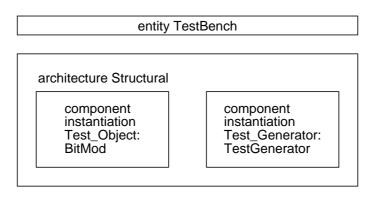

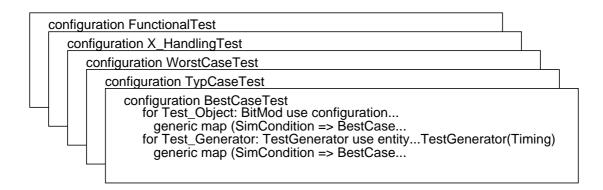

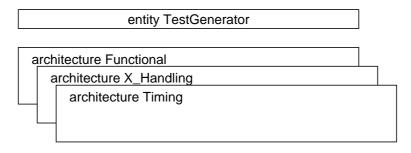

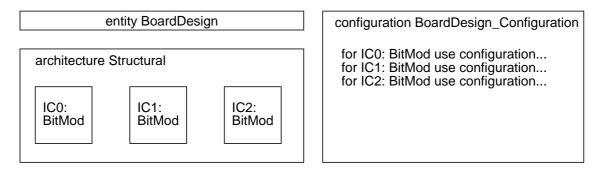

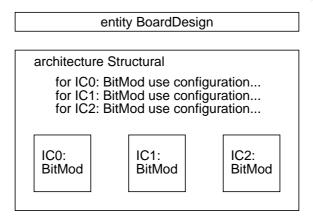

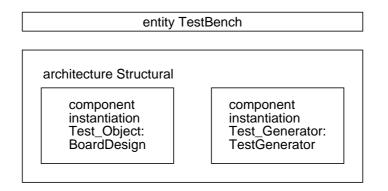

When a model has more than one hierarchical level the subcomponents should be explicitly bound using a configuration declaration, never relying on default binding. The generics of the subcomponents should be associated to the corresponding generics of the preceding entity as shown for *InstancePath* in example 1. Each component declaration should have the same name, generic and port declarations as the corresponding entity. Configuration specifications in the architecture should be avoided, permitting the usage of the more flexible configuration declarations outside the model.

```

library BitMod_Lib;

configuration BitMod_Configuration of BitMod is

for BoardLevel

for FunctionalCore: BitMod_Core

use entity BitMod_Lib.BitMod_Core(Behavioural)

generic map(InstancePath => InstancePath);

end for;

end for;

end BitMod_Configuration;

```

**Example 1:** Configuration declaration for a model for board-level simulation.

#### **3.2** Functional modelling

Functional modelling comprises in this context the part of the model representing the logical functions of the modelled component. The following sections will describe how to develop a model with high functional accuracy and good simulation performance, being two important characteristics of models for board-level simulation.

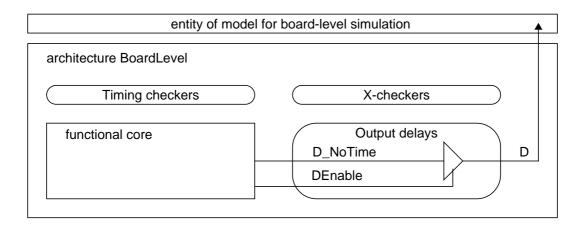

The functionality of the component should be contained in the functional core of the model for board-level simulation. It should be independent of the top-level architecture, although some functions normally implemented with tristate buffers in a component could be modelled outside the functional core, as shown in figure 4. The functional core should be modelled with zero delay on outputs and without internal signal delays if possible.

**Figure 4:** *Implementation of tristate buffer in the top-level architecture.*

#### **3.2.1** Modelling for functional accuracy

Models for board-level simulation have to reflect the functional behaviour of components accurately enough to allow board designs to be verified for functionality and timing. Simulating boards using models with high functional accuracy will reduce the number of errors found on the manufactured board. Errors not found in the simulation, located in the models or in the board design itself, will eventually be discovered in the real hardware.

There are two major approaches to modelling for board-level simulation; independently develop the model from a Functional Specification or Data Sheet, or enhance the RTL model. The first approach is necessary when no RTL model is available to the developers. It can also be the case when the model for board-level simulation is developed in parallel with the component. The component development could then benefit from the independent interpretation of the specification. The two models should be compared to each other, first visually and later automatically when both mature. In the second approach, when a RTL model is to be revised to fulfil the requirements posed on models for board-level simulation, the protection of the design should be addressed since the resulting model could possibly be synthesised. Many of the suggestions in section 3.2.2 describing how to model for simulation performance will often reduce the probability that a component could be reverse engineered.

Care should be taken when a model is developed using only a Data Sheet as input, since the component is not always described in a Data Sheet as actually being implemented. The information in the Data Sheet could have been simplified, e.g. the description of an interface protocol may be more constrained than the actual design requirements. The source describing the functionality from which the modelling is performed should be identified. Any unresolved issues should be submitted to the foundry or company supporting the component and be documented.

It is not always obvious whether to model the behaviour that is described by the *component model* or the Data Sheet when there are inconsistencies between them. It may be that some functionality of the *component model* has been simplified or omitted in the Data Sheet, e.g. proprietary design features. In such a case it is recommended to model the full functionality and issue a warning when used, instead of excluding the function and consequently have an incorrect simulation.

The inclusion of unsupported or undocumented functionality of the component in the model for board-level simulation could simplify its comparison versus the *component model*, using the same set of stimuli. The model should therefore always reflect the component behaviour when there are inconsistencies or differences between the Data Sheet and the *component model*, otherwise the deviations will possibly turn up as failures when breadboarding.

Independently of how the model is developed, the full functionality should be modelled and verified versus the *component model* when available, as per section 4.

#### **3.2.2** Modelling for simulation performance

The performance of present workstations and VHDL simulators provides a means for simulating board designs comprising several complex components such as microprocessors and ASICs. However, to be able to tap this simulation performance the simulation models have to be efficiently coded for simulation. An absolute requirement on simulation performance for models intended for board-level simulation cannot easily be defined, although unnecessarily slow or cumbersome implementations should be avoided.

The guidelines presented below are based on experiences with modelling and using models for board-level simulation. This is not an exhaustive list of issues to be addressed when a model is tuned for simulation performance. It should also be remembered that each suggestion might not be true for all situations and simulators. The best advice on simulation performance modelling is to use common sense in case of uncertainty. A good way to choose between two approaches is to simulate both and to select the one being most efficient. The stimuli used for such comparative simulations should be based on possible and probable input to the model. Different simulators have different performance characteristics, for obtaining the complete picture simulations should be performed on all foreseen simulators to be used.

Many rules and techniques that apply to writing optimised software, such as loop unrolling, code in-lining etc., also apply to models with good simulation performance since VHDL has many characteristics of a programming language. Some VHDL simulators have less built-in optimisation capabilities than state of the art optimising compilers for software, it is therefore often beneficial to manually perform optimisation at the source code level.

Standard packages, such as the *IEEE.Std\_Logic\_1164* and *IEEE.Vital\_Timing IEEE.Vital\_Primitives*, are sometimes accelerated for simulation performance. But since this is not always the case, it could be necessary to assess whether to use other types or subprograms when simulation performance is an issue.

#### 3.2.2.1 Processes

Each process invocation has a cost in terms of simulation performance and in principle the number of processes should therefore be kept small. Each concurrent assignment is treated as a process, and should be avoided where possible. Note that block and generatestatements can incur the same cost as processes.

Processes should use sensitivity lists that can be statically allocated and have therefore potentially better simulation performance than when using wait-statements that are allocated dynamically. Process invocation should be minimised, only essential signals should be included in the sensitivity list. Functions sensitive to the same signals should be grouped in the same process, reducing the number of processes to invoke for each signal event. Following the approach above, all functions related to the same clock should be grouped together. One process per clock region could be used when multiple clocks exist for the component. Functions related to different clock regions should be placed in different processes, not to invoke the process for each event on the irrelevant clocks. This approach has been found efficient when clocks have dissimilar switching frequencies.

It should be decided whether to use single or multiple processes and which signals to include in the sensitivity lists when modelling combinational and asynchronous logic, based on comparative simulations. Combinational logic only related to a single clock signal should be included in the process modelling that clock region.

Code blocks, such as checkers and autonomous functions that can be disabled by means of generics or mode pins, could benefit from being placed in separate processes using generate-statements to prevent them from executing in modes when not needed. It is not sufficient to place such functions in a process and protect them with a conditional statement, since the process will still be invoked each time there is an event on signals in the sensitivity list. The generate-statement around the process will exclude the process from the simulation when disabled, eliminating all invocation costs when not used.

The outline of the functional core architecture shown in example 8 represents such structuring. The architecture in the example is divided in two processes, representing the synchronous and the asynchronous regions of the component. The sensitivity lists of the processes have been kept short to avoid unnecessary invocations.

The synchronous region in the example is clocked by the *Clk* input and is reset by the *Reset\_N* input. The *ClkRegion* process implementing this region is made sensitive only to these two signals. The first part of the process handles the asynchronous reset of the region. The succeeding two parts model the functionality related to the rising and falling *Clk* edges. An edge on the *Clk* input is detected using the functions *Rising\_Edge* and *Falling\_Edge*, which also handle unknown input values.

The last part of the *ClkRegion* process is only invoked when no reset has been issued and neither of the clock edges have been detected. It is used for detecting and reporting unknown values on the *Clk* input as described in section 3.3.2. This method for checking for unknown input values will only negligibly contribute to the performance penalty, compared to checking the clock input at each signal event which occurs frequently.

The process *AsynchronousRegion* implementing the asynchronous region is made sensitive only to those inputs directly affecting its behaviour. The inputs  $CS_N$  and  $RW_N$  control the asynchronous write accesses to internal registers and are therefore included in the sensitivity list. The data and address buses are latched on the rising  $CS_N$  edge as shown in example 3, and do not affect the process when changing values. They need therefore not be sensed by the process and are not included in the sensitivity list, allowing for better simulation performance than if they were included. This modelling is inexact since the accessing scheme has been somewhat simplified.

#### 3.2.2.2 Signals

Variables should be used instead of signals wherever possible, since each signal requires one or several drivers, specific handling (event scheduling,) and memory storage, which takes more instructions to execute (and likely decreases the cache hit ratio). Signals should preferably be used only for communication between processes. VHDL '93 shared variables could potentially be used instead of signals, but should be used with precaution since potentially introducing indeterministic behaviour in the simulation. Another reason for merging processes is that the number of signals used for the communication between them is consequently reduced.

Resolved types should be avoided internally in the model where possible, since the calculation of the resulting value will need to call a resolution function for each event on the driving signals. Using unresolved types instead could potentially increase the simulation performance. Resolved types should therefore only be used when the resolution function is needed. This does not apply to variables, since no resolution function is needed and there should be no difference in simulation performance.

It has however been observed that there is no significant difference between using *Std\_ULogic* instead of *Std\_Logic*, since the latter is accelerated in some simulators. Some simulators also ensure that the resolution function is not invoked for signals with only one driver. This can be seen as analogous to replacing such signals with their unresolved base type, e.g. *Std\_Logic* signals with one driver becomes *Std\_ULogic* signals. An additional benefit of using unresolved types is that unwanted short-circuit connection between signals is automatically detected at analysis time since a signal of an unresolved type can only have one driver.

When moving a concurrent signal assignment into a process, it should be ensured that it is not updated more often than it would had been as a concurrent assignment. Reassigning a signal its current value should be avoided, since each such assignment requires that a transaction is scheduled for that signal. One should also be careful not to recalculate a signal value expression too often when moving the signal assignment into a process, e.g. for each clock cycle instead of each time one of the relevant input signals changes. In such case the simulation performance will decrease due to the increase of unnecessary calculation, even if the same calculated value is not reassigned to the signal. Similarly, removing static signals that seldom change will not improve the simulation performance significantly or will even decrease it.

Signal generating attributes such as '*Stable* should be avoided since they result in the creation of implicit signals which have to be handled in the scheduler. Instead should the attribute '*Event* be used where possible.

#### 3.2.2.3 Types

Numerical data types such as *Integer* normally result in better simulation performance than arrays such as *Std\_Logic\_Vector* and *Bit\_Vector*, and could be used for extensive calculations directly using the arithmetics of the processor on the host machine. However, one should be careful when the bit field information is required in the simulation, e.g. during instruction decoding in microprocessor models, since retrieving such information from an *Integer* could potentially be more costly than using an array in the first place. A trade-off should be performed between the cost for: performing type conversions between *Std\_Logic\_Vector* and *Integer*, and subsequent calculations using *Integer*; or directly performing calculations on *Std\_Logic\_Vector*. Findings indicate that the time required for converting a *Std\_Logic\_Vector* signal to an *Integer* variable, adding two *Integer* variables, and to convert the result back to a *Std\_Logic\_Vector* variable is faster than to make an addition between two *Std\_Logic\_Vector* signals.

The computations on data and address in example 3 are made using the type *Integer* instead of *Std\_Logic\_Vector* (not shown). The conversion is made directly from *Std\_Logic\_Vector* to *Integer* with the custom made function *To\_Integer*, which is only called when the value is needed. This function also checks for unknown values and issues assertion reports when detected, its declaration is shown in example 2.

```

--- Converts unsigned Std_Logic_Vector to Integer, leftmost bit MSB

-- Error message for unknowns (U, X, W, Z, -) being converted to 0

function To_Integer(

constant Vector: Std_Logic_Vector;

constant VectorName: String := "";

constant HeaderMsg: String := "To_Integer:";

constant MsgSeverity: Severity_Level := Warning)

return Integer;

```

**Example 2:** Declaration of a Std\_Logic\_Vector to Integer converter function taking into account unknown values on the input.

Type conversions on input signals should be performed in the functional core where the actual value is needed and only when necessary, and is described further in section 3.3.2. To illustrate this, the conversion between *Std\_Logic\_Vector* and *Integer* and the checking for unknown values on the data and address buses in example 3 are only necessary when the values are latched. No type conversion is therefore necessary in the top-level architecture for the two buses. This scheme has better simulation performance than if each signal would be type converted each time there is an event. Unnecessary assertion reports are also avoided since checking for unknown values is only done when the value is used.

It has been seen that enumerated types have better simulation performance than array type, especially for coding of finite state machines using case-statements, where *Bit\_Vectors* and *Std\_Logic\_Vectors* are slower than enumerated types.

```

_____

-- Implementation of all asynchronous functionality.

-- Latching of data to be written into the internal registers.

-- Generation of external data bus enable. Checks for unknown

-- values are done for the input signals.

-- The modelling is not fully correct w.r.t. a typical

-- RAM I/F, since some relaxations have been introduced.

_____

_____

AsynchronousRegion: process(CS_N, RW_N, Reset_N)

begin

if Reset_N = '0' then

-- To_X01 on Reset_N is done in the top-level architecture

-- Asynchronous reset of model

DEnable <= False;</pre>

elsif Rising_Edge(CS_N) then

-- End of access

if To_X01(RW_N, "RW_N", InstancePath, Error)='0' then

-- Write access to internal registers

-- X on CS_N is treated as no event (no access)

-- X on RW_N is treated as 1 (no write access)

-- X on A and D_In are treated as 0

-- A and D_In are converted to Integer

AWrite <= To_Integer(A, "A", InstancePath, Error);

DWrite <= To_Integer(D_In, "D", InstancePath, Error);</pre>

end if;

DEnable <= False;</pre>

elsif Now /= 0 ns then

-- Asynchronous behaviour

-- Enabled for read cycles after Reset

-- X on RW_N is treated as 0

-- X on CS_N is treated as 1

DEnable <= (To_X01(RW_N, "RW_N", InstancePath, Error)='1') and</pre>

(To_X01(CS_N, "CS_N", InstancePath, Error)='0') and

(Reset_N='1');

end if;

end process AsynchronousRegion;

```

**Example 3:** Implementation of asynchronous write access to internal registers.

When modelling large memory elements the memory actually used by the simulator on the host machine should be taken into account, since the cache hit ratio will decrease with larger memory usage, and as a consequence the simulation performance will be decreased as well. Note that it is not the size of the memory being allocated by the simulator that is critical, but the size and the distribution of the memory which is being frequently accessed. Since the allocation of the modelled memory into the actual memory differs between simulators, operating systems and hardware, it is difficult determine what impact the method chosen will have on the simulation performance. But, as a general recommendation the memory usage should be minimised as much as possible. Also from a memory usage point of view signal declarations are more costly than variable declarations.

For example, an eight bit wide register would at least require 48 bits of memory if modelled as a *Std\_Logic\_Vector* since each bit would be represented as 4 bits in memory, covering all nine *Std\_Logic* strengths. The same register contents could be represented as an *Integer* and would then require 4 bytes in most simulators, which is less than the *Std\_Logic\_Vector* representation, but which cannot represent all the nine *Std\_Logic* strengths. The memory usage should be measured for the two approaches and be used, together with the requirements on the level of detail for the data representation, for deciding on how to model such registers.

#### 3.2.2.4 Subprograms

Passing large data structures as parameters to subprograms decreases the simulation performance when the data structure size increases, which should be considered when deciding whether to represent data as *Std\_Logic\_Vector* or *Integer*. In addition, calls to subprograms declared in packages are difficult to optimised by the analyser since the package body can be reanalysed without necessitating that the code where the call is made from is reanalysed as well. It is therefore necessary to manually replace subprogram calls by in-line coding in the source code when optimising a model for simulation performance.

#### 3.2.2.5 Expressions

Globally static constants, such as deferred constants, cannot be evaluated at analysis time by the analyser. A way to work around this is to declare a local constant that is computed once during the elaboration from the deferred constant or constants, e.g. "**constant** *LocalTpd*: *Time* := *GlobalTpd* /2;" where *GlobalTpd* is a deferred constant.

It is believed that some simulators do not optimise expressions for common terms and it is therefore necessary to manually make the optimisation in the code, as in example 4.

| Original code:    | Optimised code:     |

|-------------------|---------------------|

| Result0 := A+B*C; | Temp0 := B*C;       |

| Result1 := D-B*C; | Result0 := A+Temp0; |

|                   | Result1 := D-Temp0; |

**Example 4:** *Common term in expressions being expressed as a temporary variable.*

On the other hand, unnecessary usage of temporary expressions could potentially reduce the simulation performance since each temporary variable assignment has a certain cost, as shown in example 5. Needless to say is that when performing calculations with temporary signals instead of variables, the penalty is worse.

```

-- Original code: -- Optimised code:

Temp1 := A+B; Result2 := (A*B)/(C*D)*(E mod F);

Temp2 := C-D;

Temp3 := E mod F;

Result2 := Temp1/Temp2*Temp3;

```

**Example 5:** Unnecessary temporary expressions merged into one.

Since VHDL specifies short-circuit boolean evaluation, terms that would short-circuit an expression evaluation should be placed as early as possible in the expression. Short-circuit evaluation is specified for the types *Boolean* and *Bit*. The logical operators (**and**, **or**, etc.) do not evaluate short-circuit for *Std\_Logic*, but can be exploited as in example 6. The two signals *A* and *B* are of type *Std\_Logic*, but each expression within the parenthesis will result in a *Boolean* value, and the or-operator could thus benefit from short-circuit evaluation in case the first parenthesis result is *True*.

```

signal A, B: Std_Logic;

...

if (A='1') or (B='0') then

...

end if;

```

**Example 6:** *Expression with potential short-circuit evaluation.*

#### 3.2.2.6 Conditional statements

A fundamental rule when modelling for simulation performance using VHDL is to only execute code when necessary. Therefore, conditional statements should be used to reduce unnecessary execution of code. The outer conditional statement should reduce the necessity to evaluate enclosed conditional statements, based on an assessment on how often subsequent code needs to be executed. This is done by using nested if- and case-statements, ordered so that the branches with the highest probability are executed first. Conditional expressions in the statements should be ordered for maximum boolean short-circuit evaluation and the complexity should be minimised. Efficiency of conditional statement structures can be analysed using code coverage results. It has been shown that an assignment of a signal is between one and two orders of magnitude more costly in terms of simulation time compared to reading a signal or variable in an if-statement. This suggests that one can use large structures of if-statements to prevent a signal to be unnecessarily assigned, and still gain in simulation performance.

It can be seen in example 3 that the if statements have been nested. The conditional expression in the outer if-statement is the *Rising\_Edge* function. The conditional expression in the inner if statement is a custom made *To\_X01* function that will detect and report unknown values on the input.

The *Rising\_Edge* function is believed to execute faster than the custom *To\_X01* function, since it is accelerated in most VHDL simulators, and is consequently placed in the outer if statement that will be executed more frequently. The two conditions are not combined in one expression, not to evaluate any part of the expressions unnecessarily.

The *DEnable* signal in example 3 is used for enabling the tristate buffer isolating the outgoing  $D_Out$  bus from the external port D in the top-level architecture. The type *Boolean* was being simple to use in if statements and could potentially simulate faster than *Std\_ULogic*. Its usage in the top-level architecture is described further in example 22 and figure 4.

#### **3.2.3** Evaluation of simulation performance

The simulation performance of a model should be evaluated continuously during the development to identify simulation bottlenecks and accordingly modify the code for improvements. An analysis of the simulation speed should compare the model intended for board-level simulation and the actual hardware performance, stating the relative simulation performance measured in terms of instructions per second, etc.

The test suite used for this purpose should have a low influence on the performance measurements, but should also reflect realistic simulation scenarios and execute large portions of the model. The measurements should be compared for different simulators and platforms when possible, avoiding simulation pitfalls.

A code coverage utility is a useful means for identifying simulation bottlenecks during model development. The output from such tools usually states the number of times each statement in the source code has been executed during a simulation, allowing an identification of statements frequently executed.

Simulation performance can often be improved by reordering the code or modifying the structure of the conditional statements. It is also possible to identified redundant and unnecessary code that could complicate maintenance.

The Coverage utility in the Synopsys® VSS simulator records the number of times a statement is executed when running a particular simulation. The Leapfrog® VHDL simulator from Cadence has been announced to includes a code profiler, comparable with the Coverage utility, but which also identifies where in the code most of the simulation time is spent.

The VHDLCover<sup>TM</sup> tool is a simulator independent coverage utility, that adds VHDL code to the model which can then be simulate on any VHDL simulator, and the results can be further analysed the tool. This tool claims to analyse branches taken and other things besides the executed statement count.

#### **3.2.4** Outline of entity and architecture declarations for functional cores

The entity of the functional core should have the same name as the model for board-level simulation but with *\_Core* suffixed when only one entity is needed. The architecture name should reflect the nature of its contents: *Behavioural* or *Structural*. When multiple entities are used for the functional core they should be named after their function. If a three-level hierarchy is needed, the name of the second level should have *\_Core* suffixed. The *InstancePath* generic should be passed down the hierarchy where the checkers are implemented. The default value should then be the same as the name of the corresponding entity, which will not appear in an assertion report when the *InstancePath* is passed down correctly. It should only be used for sub-module verification during the development.

The entity shown in example 7 has ports of type  $Std\_ULogic$  since no tristate drivers are implemented in the functional core. No type conversion is needed in the top-level architecture between the  $Std\_Logic$  ports of the top-level entity and the  $Std\_ULogic$  ports of the functional core, since they are equivalent and compatible. Ports of  $Std\_Logic\_Vector$  type have not been converted to the unresolved  $Std\_ULogic\_Vector$  type in the top-level architecture. It is done in the functional core where and when the value is truly used and the ports are therefore of type  $Std\_Logic\_Vector$ . The output port  $D\_Out$  of type Integer is converted to  $Std\_ULogic\_Vector$  in the top-level architecture only when its value is used, and is therefore not converted in the functional core.

```

library IEEE;

use IEEE.Std_Logic_1164.all;

entity BitMod_Core is

generic(

InstancePath: String := "BitMod_Core:"); -- For assertions

port(

-- System signals

Test0: in Std_ULogic;

-- Test mode

Clk: in Std_ULogic;

-- Master Clock

Reset_N: in Std_ULogic;

-- Master Reset

-- Interface to internal registers

A:inStd_Logic_Vector(0 to 1);--Address busCS_N:inStd_ULogic;--Chip selectRW_N:inStd_ULogic;--Read/write

D_In: in Std_Logic_Vector(0 to 7); -- Data bus input

D Out: out Integer range 0 to 255;

-- Data bus output

DEnable: out Boolean;

-- Data bus enable

-- Serial Interface

SClk: in Std_ULogic;

SData: in Std_ULogic;

MData: out Std_ULogic);

-- Serial clock

-- Serial input

-- Serial output

end BitMod_Core;

```

**Example 7:** *Outline of a functional core entity for a model for board-level simulation.*

All scheduling of output delays and timing checking are performed in the top-level architecture. All type conversions and checking for unknown value on the input ports are performed in the functional core, except the static signals *Reset\_N* and *Test* that are converted in the top-level architecture.

The outline of the functional core architecture in example 8 covers some aspects of modelling for functional accuracy and simulation performance described earlier. The *ClkRegion* process covers all functionality related to the *Clk* input and is only made sensitive to the *Clk* and *Reset\_N* inputs, being asynchronously reset by *Reset\_N*. An if-statement divides the process in four regions: reset of the process, functionality related to the rising *Clk* edge, functionality related to the falling *Clk* edge, and checking for unknown values on *Clk* when neither in reset nor an edge is detected.

The AsynchronousRegion process includes all asynchronous functionality in the example and is made sensitive to Reset\_N,  $CS_N$  and  $RW_N$ , which are the only inputs that can induce any changes on the outputs due to an event. An if-statement divides the process in three regions: reset of the process, functionality related to the rising  $CS_N$  edge and functionality related to  $RW_N$  input when there is no rising  $CS_N$  edge.

```

architecture Behavioural of BitMod_Core is

-- Local signal declarations.

begin

-- Implementation of all functionality driven by Clk

ClkRegion: process(Reset_N, Clk)

begin

if Reset_N = '0' then

-- Asynchronous reset of model

elsif Rising_Edge(Clk) then

-- Rising Clk edge region

elsif Falling_Edge(Clk) then

-- Falling Clk edge region

else

-- Check for unknown Clk value, since the model is not

-- being reset and neither rising nor falling Clk edge

-- is detected.

-- No assertions at start up of simulation

assert not (Is_X(Clk) and (Now /= 0 ns))

report InstancePath & " 'X' on Clk input"

severity Error;

end if;

end process ClkRegion;

-- Implementation of asynchronous functionality

AsynchronousRegion: process(Reset_N, CS_N, RW_N)

begin

if Reset N = '0' then

-- Asynchronous reset of model

else Rising_Edge(CS_N) then

-- Asynchronous behaviour related to CS_N

else

-- Asynchronous behaviour related to RW_N

end if;

end process AsynchronousRegion;

end Behavioural;

```

# **Example 8:** *Outline of a functional core architecture for a model for board-level simulation.*

#### **3.3** Interface modelling

Models having similar user interfaces for simulation condition selection, the same type and format of error messages etc., provide the user with a single interface to learn and understand. The model interfaces in this document have been made as simple as possible, without necessarily sacrificing the potential of the language, promoting their usage by others than experienced VHDL users.

The following interface modelling aspects are covered in this section:

- Definition of timing parameters;

- Checking for timing constraint violations;

- Scheduling of output delays;

- Management of unknown input values;

- Reporting of model messages.

#### 3.3.1 Timing modelling

In the VHDL Modelling Guidelines, RD1, the timing modelling concept is based on the IEEE VHDL Initiative Toward ASIC Libraries activity, VITAL, as described in RD4. This allows the VITAL subprograms to be reused, saving coding effort as well as potentially offering high simulation performance since several simulators already provide accelerated versions of VITAL subprograms.

Full VITAL compliance has not been achieved since a different technique for the selection of the simulation conditions (e.g. minimum or maximum delay) has been specified. VITAL is based on using an external delay calculator, where the actual timing values for a specific simulation condition are back-annotated using the Standard Delay File format, SDF, which is well adapted for simulation of ASICs.

The ESA timing modelling concept defines the notion of an operating point and provides a single generic with which a user can change the simulation condition for all components.

For models intended for board-level simulation developed for ESA the selection of the simulation condition should be controlled by the *SimCondition* generic of type *SimConditionType* declared in the package *ESA.Simulation*, and should have the default value *WorstCase*. The generic *TimingChecksOn* of type *Boolean* should be used for disabling the timing checkers and should have the default value *False*.

It is recommended to only report timing violations and not to generate unknown values on the outputs. In case it is implemented, the *XGenerationOn* generic of type *Boolean* with the default value *False* should be declared in the top-level entity declaration, disabling generation of unknowns when set to *False*, which should also be the default value. Generation of unknown values on outputs is usually only implemented for components with low complexity where the propagation of the unknown values could be useful to follow and analyse. Note that the VITAL specification uses the name *XOn* instead of *XGenerationOn*. Normally, the following generics should not be needed. The generic *XChecksOn* of type *Boolean* should be used for disabling the checking for unknown input values, and should have the default value *True*. The generic *MsgOn* of type *Boolean* should be used for disabling the generation of messages from timing checkers, which could be used in conjunction with *XGenerationOn* when only unknown values on the outputs are wanted, and should have the default value *True*.

Since models developed following the proposed scheme are not VITAL compliant, the VITAL compliance checkers possibly found in VHDL analysers should be switched off not to generate unnecessary warning and error messages during the analysis. No back-annotation should be performed using SDF and the negative constraint calculation phase, as specified in RD4, should be disabled not to change the generics used for negative setup and hold constraints as described further in section 3.3.1.2.1.

The two attributes *Vital\_Level0* and *Vital\_Level1* defined in RD4 should not be used since models for board-level simulation using *ESA.Simulation* are not compliant with either.

#### 3.3.1.1 Timing parameters

The timing parameters should preferably be of the *Time Array* types declared in the packages *ESA.Simulation* and *ESA.Timing* defined in appendix C, supporting most of the types declared in *Vital\_Timing* used for timing information. The *Time Array* types are all indexed by the type *SimConditionType*, as shown in example 9, making it possible to select the value corresponding to the simulation condition, which is performed in the top-level architecture. There is no need for having a *Time Array* with *VitalDelayType* elements since they are equivalent to the type *Time* for which a *Time Array* type is already declared in the package *ESA.Simulation*.

The two packages *ESA.Simulation* and *ESA.Timing* should never be redefined or moved to a different library since the intention is to provide only one format for the selection of simulation condition for all models, normally originating from different developers.

```

-- Definition of the SimConditionType type

type SimConditionType is (WorstCase, TypCase, BestCase);

-- Definition of Time Array type, used with Time.

type TimeArray is array(SimConditionType) of Time;

-- Definition of Time Array types, used with Vital Delay Types.

type TimeArray01 is array(SimConditionType) of VitalDelayType01;

type TimeArray01Z is array(SimConditionType) of VitalDelayType01Z;

type TimeArray01ZX is array(SimConditionType) of VitalDelayType01ZX;

```

**Example 9:** Contents of the Simulation and Timing packages.

The intended purpose of the *Vital Delay Array Types* declared in *Vital\_Timing* is for specifying the timing for each individual element of an array, such as for data or address signals, and should never replace the usage of the *Time Array* types declared above, since they are indexed with the subtype *Natural* and not the required *SimConditionType*.

european space agency

No *Time Array* types have been declared in package *ESA*.*Timing* for any of the *Vital Delay Array Types*, since it is not possible to define a constrained array of unconstrained arrays.

The level of detailed timing information that is represented by the *Vital Delay Array Types* is not necessary for most models. Should such detailed timing information be necessary, the required declarations should be done for those array widths needed and placed in the timing package of the model. Example 10 shows a declaration of a *Time Array* type with *VitalDelayType01ZX* elements that is used for holding timing information related to a *Std\_Logic\_Vector(0 to 7)* port.

**Example 10:** Declaration of Time Array type for a port with individual timing on each of the eight elements, supporting the full Vital Transition Type range.

The timing parameters needed by the model should be declared in a separate timing package as a deferred constant as it has been shown in example 11. The package body can then be modified if necessary and analysed without the need to re-analyse the complete design, which can be necessary when new data from foundries become available. This also eases distribution of analysed models.

The timing parameters in the timing package can be used directly in the top-level architecture or be passed via generics to the model. The latter option permits the user to modify the timing parameters for each individual component instantiation by using generic maps, useful e.g. when modelling large capacitive loads on boards.

```

library ESA;

use ESA.Simulation.all;

use ESA.Timing.all;

package BitMod_Timing is

-- Deferred constants for the timing parameters.

. . .

constant tpd_Clk_MData: TimeArray01;

-- T9

. . .

end BitMod_Timing;

package body BitMod_Timing is

constant tpd_Clk_MData: TimeArray01 :=

-- T9

((25 ns, 24 ns),

-- WC

(11 ns, 13 ns),

--TC

-- BC

(7 ns, 8 ns));

. . .

end BitMod_Timing;

```

**Example 11:** Package containing timing parameters declared as deferred constants.

The constants in the timing package and the generics in the entity declaration can have the same names due to visibility rules in the language. It is therefore no need to have suffixes such as *\_Default* attached to the constant names.

Timing parameters should have names compliant with RD4, or alternatively use names from the Data Sheet. It is recommended that timing parameters containing signal names with underscores should be written without them. For example, a timing parameter for the signal *CS\_N* could be written as *tperiod\_CSN*, which is compliant with RD4. The timing parameter suffixes defined in RD4 should be used where applicable: *posedge* for rising signal edges, *negedge* for falling signal edges etc.

The timing parameters should be given in an integer number of nanoseconds with values rounded in a pessimistic way, to avoid simulation time limitations. Simulators supporting 64 bit implementation of the time counter support approximately 300 years of simulation time with a resolution of 1 ns, and 32 bit implementations support only 2 seconds but should be sufficient for limited hardware and software co-simulation.

### **3.3.1.2** Timing constraint checking

All timing constraint checkers should be contained in the process *TimingCheck* in the toplevel architecture, as outlined in example 12, but the process could be divided for performance reasons when found beneficial. The processes should be sensitive to all signals checked or referenced. All code in the process should be possible to disable with the *TimingChecksOn* generic and a generate-statement, also shown in example 12, to reduce the performance penalty when not used. This outline supports only positive constraints, a version supporting negative constraints is shown in example 16. Timing parameters to be checked should be assigned to the subprogram formals using named association, indexed by the *SimCondition* generic to allow selection of timing parameter values corresponding to the simulation condition as shown in example 15.

Timing constraint checkers should be enabled individually when relevant for the simulation. This should be done by using the subprogram parameter *CheckEnabled*, as shown in example 15 and example 18. Note that this parameter does not prevent the checker from being executed, it only masks the assertion reports and the assertion of the *Violation* parameter in *Vital\_Timing* subprograms, and should not be used instead of the *TimingChecksOn* generic used in the generate-statement.

Care should be taken when establishing the conditions for which each checker is enabled, e.g. some checkers are not enabled during reset of the model, other checkers may only be enabled after write operations. Enabling conditions of checkers related to clock period timing constraints should be carefully modelled not to enable when not relevant to the simulation, e.g. during reset. The frequent value changes on clock inputs could cause many unnecessary subprogram invocations, decreasing the simulation performance, and should be disabled for a clock not used in some mode or similar.

Enabling of the checkers for some timing constraints could be a rather complex task, as for the setup and hold checker in example 15. The expression for the enabling variable *DataCheckEnabled* is shown in example 13. The checker is enabled when there is a falling edge on either  $CS_N$  or  $RW_N$  while the other input is asserted, which is when the registers are written. It is kept enabled until there is a falling  $CS_N$  edge while  $RW_N$  is de-asserted, which is when the registers are read. The checker will therefore be enabled at the beginning of a write access and be kept enabled until the next read access begins.

```

TimingGenerate: if TimingChecksOn generate

TimingCheck: process(Clk, SClk, D, CS_N, RW_N, Reset_N_X01)

-- Variables containing information for period checkers

-- Variables containing information for setup & hold checkers

-- Variables for enabling timing checkers

begin

-- Enabling of various checkers

-- Reset_N low time w.r.t. Clk checking

-- Register interfaces checked for illegal events etc.

-- Checkers using custom made subprograms.

PeriodCheck(...); -- SClk period

CheckWidth(...);

-- CS_N de-assertion width

-- Timing checkers using Vital_Timing subprograms.

VitalPeriodPulseCheck(...); -- Clk period, high and low times

VitalPeriodPulseCheck(...); -- CS_N width for write access=

VitalSetupHoldCheck(...); -- D setup & hold w.r.t. CS_N

end process TimingCheck;

end generate TimingGenerate;

```

#### **Example 12:** The process TimingCheck resides in the top-level architecture.

If the checker in example 13 was disabled on the rising *CS\_N* or *RW\_N* edge at the end of the write access, the hold constraint would not be checked since it is normally longer than 0 ns relative to that event. The same enabling scheme could be implemented by delaying the control signals but would have lesser performance. Note the usage of the accelerated functions *Falling\_Edge* and *To\_X01* in the example.

The type conversion is made locally in the *TimingCheck* process, since the signals are not converted in the top-level architecture but only in the functional core, and will not contribute any simulation performance penalty when timing checking is disabled. It is preferable to formulate a smart enabling condition for an accelerated *Vital\_Timing* subprogram than to develop a completely new timing checker.

```

-- Enables the setup and hold checker for D during write operations.

-- The checker is enabled when both CS_N and RW_N are asserted,

-- until the next read access begins, since the data hold constraint

-- is longer than either CS_N or RW_N is de-asserted after write.

if ((Falling_Edge(CS_N) and To_X01(RW_N)='0') or

(Falling_Edge(RW_N) and To_X01(CS_N)='0')) then

DataCheckEnabled := True; -- Enable checker

elsif (Falling_Edge(CS_N) and To_X01(RW_N)='1') then

DataCheckEnabled := False; -- Disable checker

end if;

```

#### 3.3.1.2.1 Timing constraint checking using Vital\_Timing subprograms

It is recommended that the timing checkers declared in the *Vital\_Timing* package are used. The *Vital\_Timing* procedures *VitalSetupHoldCheck*, *VitalRecoveryRemovalCheck* and *VitalPeriodPulseCheck* are declared for the types *Std\_ULogic* and *Std\_Logic\_Vector*. Note that *Std\_ULogic\_Vector* and *Std\_Logic\_Vector* are not compatible, but *Std\_ULogic* and *Std\_Logic* are, which excludes the possibility to check *Std\_ULogic\_Vector* inputs.

The *VitalSetupHoldCheck* procedure detects a setup or a hold violation on the test signal with respect to the corresponding reference signal. The timing constraints are specified through parameters representing the setup and hold times for low and high test values. This procedure assumes non-negative values for the timing constraints. The setup and hold checker shown in example 15 supports only positive timing constraint values, thus neither of the timing parameters can have a negative value.

The *VitalRecoveryRemovalCheck* detects the presence of a recovery or removal violation on the test signal with respect to the corresponding reference signal. The timing constraints are specified through parameters representing the recovery and removal times associated with a reference edge of the reference signal. This procedure also assumes nonnegative values for the timing constraints.

The *VitalPeriodPulseCheck* checks for minimum periodicity and pulse width for low and high values of the test signal. The timing constraint is specified through parameters representing the minimal period between successive rising and falling edges of the test signal and the minimum pulse widths associated with high and low values. Note that the procedure cannot be used for checking maximum period widths, when such checkers are needed they have to be developed separately. Note also that the timing parameter names defined in RD1 containing the suffixes *\_min* and *\_max* are no longer VITAL compliant, but could still be used for models intended for board-level simulation developed for ESA.

```

-- Variables containing information for checkers

variable Period_Clk: VitalPeriodDataType := VitalPeriodDataInit;

variable Period_CSN: VitalPeriodDataType := VitalPeriodDataInit;

variable Timing_D: VitalTimingDataType := VitalTimingDataInit;

```

#### **Example 14:** Initialisation of variables used by Vital\_Timing subprograms.

Variables used by the *Vital\_Timing* subprograms for storing intermediate results should be initialised as shown in example 14 for correct operation. Most *Vital\_Timing* subprograms apply implicitly *To\_X01* conversion on their inputs. It is therefore not necessary to perform any type conversions on the signals external to the subprograms, as shown in example 15. These implicit internal type conversions should be implemented in any custom developed timing checkers when possible, to have similar interfaces as *Vital\_Timing* subprograms. The severity level of most *Vital\_Timing* subprogram assertion reports can be controlled via the *MsgSeverity* parameter as shown in example 15, which makes it possible to implement timing checkers that are compliant to the scheme suggested in RD1. The *RefTransition* parameter used by most *Vital\_Timing* subprograms

european space agency

is of type *VitalEdgeSymbolType* which allows the user to specify complex signal transitions for the reference signals. The value '*R*' used in example 15 denotes any possible rising edge.

When it is chosen no to generate any unknown values on outputs at timing violations, it is sufficient to declare only one variable for all the *Violation* parameters of the timing checkers, since the value of the variable will not be used. The parameter *XOn* is used in conjunction with *XGenerationOn*, preventing an 'X' from being assigned to the *Violation* parameter when a timing violation is detected. It should have no impact when unknown value generation is not implemented.

```

VitalSetupHoldCheck(

-- D setup & hold w.r.t. CS_N

Violation => Violation,

=> Timing D,

TimingData

TestSignal

=> D,

TestSignalName => "D",

RefSignal => CS N,

RefSignalName => "CS_N",

SetupHigh => tsetup_D_CSN(SimCondition),

SetupLow

=> tsetup_D_CSN(SimCondition),

HoldHigh

=> thold D CSN(SimCondition),

HoldLow

=> thold_D_CSN(SimCondition),

CheckEnabled => DataCheckEnabled,

RefTransition => 'R',

=> InstancePath,

HeaderMsg

XOn

=> False,

MsqOn

=> True,

MsqSeverity => Warning);

```

Since the *VitalSetupHoldCheck* and *VitalRecoveryRemovalCheck* procedures accept only positive setup and hold values, the relation between the test and reference signals has to be adjusted. Negative setup and recovery times correspond to an internal delay on the reference signal. Negative hold or removal times correspond to an internal delay on the test signal.

Negative timing constraints are handled internally in the model by delaying the test or reference signals using the function *VitalSignalDelay* as shown in example 16. The *VitalSignalDelay* procedure is called in the top-level architecture to delay the appropriate test or reference signal in order to accommodate negative constraint checks. When the delays are associated with other signals they may need to be appropriately adjusted so that all constraint intervals overlap the delayed reference signals.

When negative timing constraints are to be used in a model, two extra timing parameters need to be declared for each setup and hold or recovery and removal pair. Timing parameters on the format *ticd\_<ClkPort>* should be used for declaring the time with which a reference signal should be delay, and *tisd\_<InPort>\_<ClkPort>* should be used for declaring the time with which a test signal should be delayed.

The additional local signals needed and the concurrent procedure calls to *VitalSignalDelay* should all be placed in a block statement within the generate-statement containing the procedure *TimingCheck*, as shown in example 16. It is suggested that the label of the block is named *TimingBlock*. By including the signal declarations in the block instead of in the declarative part of the architecture, the signals will not be allocated if timing checking is disabled, potentially reducing the memory usage. The block statement, the signal declarations and the delaying of the signals should only be used when negative timing values are checked, since it would else unnecessarily reduce the simulation performance.

```

-- In the timing package (and in generic declaration):

constant tsetup_IO_Clk: TimeArray := (10 ns, 10 ns, 10 ns);

constant thold IO Clk: TimeArray := (10 ns, 10 ns, 10 ns);

constant ticd_Clk: TimeArray := (15 ns, 0 ns, 0 ns);

constant tisd_IO_Clk: TimeArray := ( 0 ns, 0 ns, 15 ns);

-- In the architecture BoardLevel:

TimingGenerate: if TimingChecksOn generate

TimingBlock: block

signal IO_Delay: Std_ULogic;

-- Delayed test

signal Clk_Delay: Std_ULogic;

-- Delayed reference

begin

VitalSignalDelay(Clk_Delay, Clk, ticd_Clk(SimCondition));

VitalSignalDelay(IO_Delay, IO, tisd_IO_Clk(SimCondition));

TimingCheck: process(Clk_Delay, IO_Delay)

variable IO TD: VitalTimingDataType := VitalTimingDataInit;

variable Violation: X01

:= '0';

begin

VitalSetupHoldCheck(

Violation => Violation,

TimingData => IO_TD,

TestSignal => IO_Delay,

TestSignalName => "IO",

TestDelay => tisd_IO_Clk(SimCondition),

RefSignal => Clk_Delay,

RefSignalName => "Clk",

RefDelay => ticd_Clk(SimCondition),

SetupHigh => tsetup_IO_Clk(SimCondition),

SetupLow => tsetup_IO_Clk(SimCondition),

HoldWigh => tbald_TO_Clk(SimCondition)

HoldHigh => thold_IO_Clk(SimCondition),

HoldLow

=> thold_IO_Clk(SimCondition),

CheckEnabled => True,

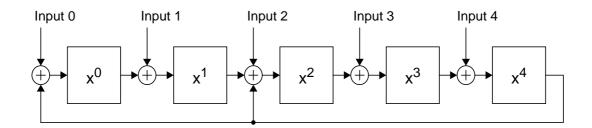

RefTransition => 'R',